This article is an excerpt from ESA SPCD 2022 paper entitled “Miniaturization of high voltage MLCC for space applications” written by Pascale ESCURE, Nicolas RUSCASSIER, Tchavdar DOYTCHINOV, EXXELIA SAS, France ( that was presented during the 4th ESA SPCD conference at ESA ESTEC, The Netherlands 11-14th October 2022. Published under ESA SPCD organisation committee permission.

INTRODUCTION

Miniaturization of equipment is a permanent challenge in the space field, for space and weight reduction. The challenge with high voltage components used in space application is a breakdown (surface arcing) that can appear at voltage below 350 V. To allow parts size reduction while maintaining optimal reliability and avoid surface arcing, varnishing or molding solutions exist for single leaded chips (Figure 1.). For stacked MLCC (Figure 2.) however, the arcing risk remains in the areas between the chips elements, because of presence of gas.

BREAKDOWN VOLTAGE IN LOW-PRESSURE GASEOUS ENVIRONMENT

According to the High voltage engineering and design handbook, the basic breakdown mechanism is caused by collision of charge carriers in the gas volume and interactions with the electrode surfaces (Townsend mechanism).

In principle, the electrical field accelerates free electrons inside gas-filled gap. These accelerated electrons are colliding with gas atoms.

If the kinetic energy of the electrons is high enough, they ionize gas atoms, releasing further electrons. An avalanche of electrons can grow towards the anode, while the ions moving in opposite direction collide with the cathode releasing new electrons. A well ionized, high conductive breakdown channel can develop in a time frame of a few microseconds. As a consequence of the avalanche breakdown, there is always an optimum, where molecule distance (given by gas pressure) and electrical field strength (given by total gap distance) are providing optimum conditions for ionisation.

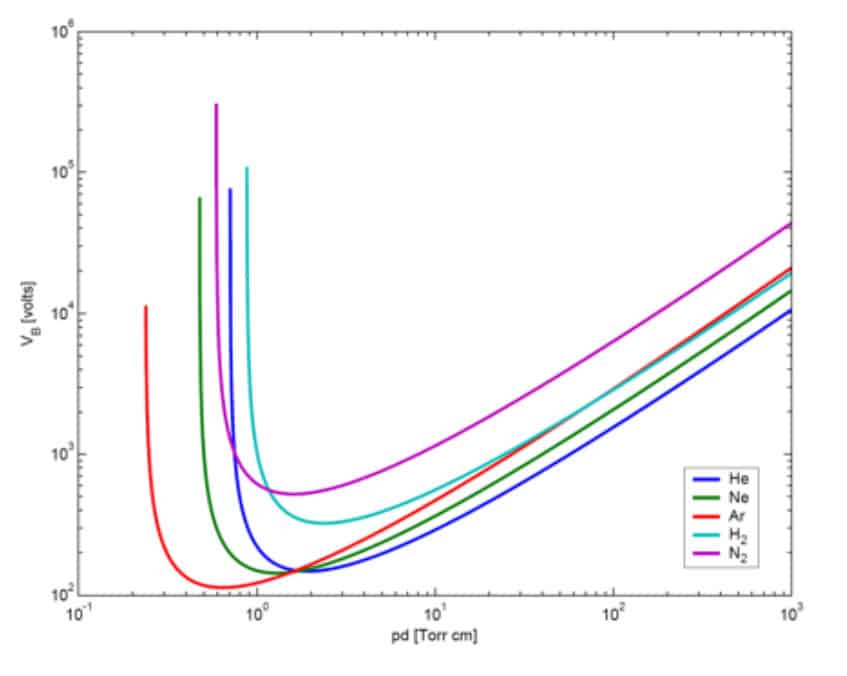

For these “optimum” conditions, the result is a very low breakdown voltage (Fig.3.). This physical relation is expressed by the “Paschen Law” and the corresponding “Paschen Curve”, which gives a breakdown voltage of 330 V. To mitigate this issue, an insulating material is applied on the surface of high voltage components.

To miniaturize a footprint, several capacitor chips can be stacked. In this case, you must be able to insure that there is no risk of arcing between the opposite poles, in the zones that cannot be protected by external potting.

SOLUTION TO PROPOSE SMALLER PARTS

The Exxelia’s solution is the second one, stacking parts to reach in a smaller case the same capacitance as the one available in single chip bigger parts as shown on Figure 2. Exxelia manage for a long time parts stacking for space application (cf to CNC5x and CNC3x high capacitance QPL series), but on low voltage parts (high capacitance series have a maximum rated voltage of 500V) or on standard parts where insulation is not mandatory required everywhere around the parts.

For space application, the main point is to find a way to ensure this insulation everywhere in the stack, in particular between the chips. Exxelia’s solution needs an ‘’interchip’’ filling material, which must be isolating, thermo-mechanically compatible with following steps of component finishing, for example lead frames soldering. It must also be compatible with customer’s use of the component.

Lead frames soldering for space applications uses High Melting Point leaded alloy, with copper silvered DIL shaped lead frames ; the reflow temperature of this alloy is 310°C, and must be processed at 400°C for hand iron soldering, with preheating of the chips to prevent thermomechanical cracks. The filling material must be applied on the chips before stacking them, to be sure to insulate their surface. It means that the chosen material must be able to support the lead frames soldering process, preheating as well as solder reflow.

We choose a glass material to do this filling role. This glass is supplied as a paste, in jars that will be transferred in a syringe to be deposed by dispensing, and we choose to use the automatic dispensing via a 4 axis dispensing robot.

GLASS DEPOSITION – EXPERIMENTAL TRIALS

First task of this project was to find the adequate way of processing the glass paste, to create an efficient inter-chip insulating barrier.

It includes:

- chips preparation : only one of the two chips to link ‘’glassed’’, both surfaces to link to ‘’glass’’

- glassing firing cycle definition : pre-firing on single chips needed (spread glass reflow cycle) or not, firing cycle definition (stacking=linking glass reflow cycle)

- tooling definition for the reflow = stacking cycle

- effect of glass filling (presence and quantity) on soldering step (stacking) and on thermomechanical behaviour of the stacks

- deposition parameters vs ink viscosity : robot cycle parameters, i.e. movements management, pressure management, syringe spindle

ELECTRICAL BEHAVIOUR SIMULATION

The aim of the study is to show pressure effect on withstanding voltage values, to validate/invalidate the Exxelia HV stacks useability for aeronautics and/or space applications. On a quite small part,2220 size, without any internal electrode (the aim here is to check external withstanding of the stacks and not internal withstanding of the dielectric), we tested withstanding voltage change between atmospheric pressure and a pressure of 200-250 mbar, which corresponds to an altitude between 10000 and 11500 meters (long flights cruise altitude). A low pressure measurement equipment has been developed in-house to generate the data.

1 – Withstanding voltage reference (under atmospheric and low pressure) :

To fix reference values, we did the withstanding voltage measurement on 2220 single bare parts (without any barrier), under atmospheric pressure and under low pressure (220-240 mbar) range:

The difference of withstanding voltage is significant: from 6500 VDC at atmospheric pressure to 2200 VDC at lower pressure.

2 – Influence of glass barrier presence on withstanding values :

On the same parts as paragraph 1, some stacks of two chips have been manufactured, with glass line barrier (parts 2-1 to 2-5) vs no barrier stacks (parts 2-6 to 2-10), and all externally covered with a silicone varnish (aerosol deposition) to simulate customer potting (external leakage prevention). Only low pressure measurements have been performed.

Withstanding voltage values are globally higher on stacks with glass barrier than without. Another run of trials has been performed on similar 2 chips stacks, with glass barrier or not, with no varnish, to try to localize the leakage when occurring, with insulation of the end terminations:

* the arcing on the surface of the glass occurs on the side of the stacks: the electrical arc goes around the glass barrier.

It is clear with this measurement configuration that glass barrier is efficient. The low pressure withstanding values of stacks with the glass barrier (parts 3-1 to 3-10, table 3) are similar to the reference ones at atmospheric pressure (parts 1-1 to 1-5, atmospheric values, table 1): no breakdown till maximum voltage delivered by test equipment (6500 VDC). On some parts, a leakage occurred at the surface of the glass (unvarnished surfaces on the sides of the stacks), which wouldn’t occur with an external potting.

Very low pressure measurement performed on part 3-3 (21mbar) also shows that it’s efficient for space conditions environment: the arcing occurred between the clamps and not on the parts. It means that the glass line deposed between the opposite poles acts as planned as a protective barrier, which improves breakdown voltage of the stack under low pressure.

CONCLUSION

Exxelia’s solution to manufacture reliable HV stacks useable in aeronautics and space conditions seems to work regarding presented results. It is a promising technology to decrease capacitor footprints in space applications. Exxelia is performing additional studies (including CSAM observations) to confirm this technology on various configurations (ceramics, sizes and thicknesses of the chips) and, also, on functional HV parts (with electrodes) before qualification and release to customers.