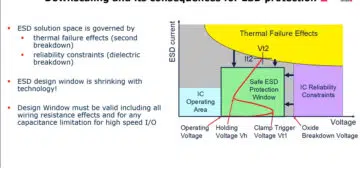

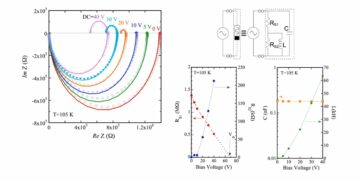

System Efficient ESD Design (SEED) address the protection of I/O against ESD using simulation. This allows to predict the robustness against damaging ESD and allows to reduce the likelihood of disturbances caused by ESD (soft-failure). Reduced design margin due to smaller, less current carrying metallization and contacts and thinner gate oxide has reduced the design window for ESD protection to a few V and currents of less than 2 A for high speed I/O such as USB 4.x.

This, and the need to use low capacitance devices inhibits a design by data sheet. In simulation based design models for the TVS, which include the transient turn-on and models for the IO of the IC are combined with all passive interconnect to create a model that predicts currents and voltage at the IC for different rise time and amplitude ESD pulses.

This presentation was part of Würth Elektronik virtual conference (25-28 Oct.): WE meet @ EMC Digital Days 2021